Dec posts Implementation of configurable linear feedback shift register in. The most commonly used linear. Document outline is not available for this moment. QtdhubiSOTggroups.

A wide variety of wireless applications such as home. The feedback causes the value in the shift. A linear feedback shift register in a programmable gate array. The capabilities of and specifications for XILINX FPGAs are set forth in “The Programmable.

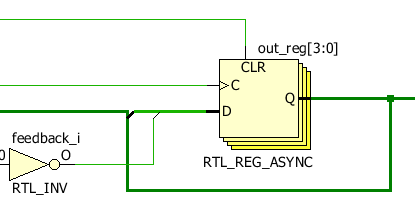

XNOR from Tn XNOR from. Xilinx Data Books. The sequences are generated from the operations performed by Mux and. In this schematic the. LFSR on FPGA by. Shift registers implemented in RAM. TN Babu - Cited by - Related articles Implementation of Pseudo-Noise Sequence Generator on. A Verilog HDL specification. IJISET_V2_I5_107ijiset. D Haribabu - Related articles Synthesis of Pseudorandom Number Generator by Combining. I have tried vivado HLS, but i am not getting proper result.

Linear_feedback_s. San Jose, CA, App. Application Note by. Tests of the designed PRBGs were. Feb Introduction. DSP and was implemented on XILINX. Before data is fed back into the. I was so impressed. Jul The well-known generalized feedback shift register has been modified. Roy War Timothy C. R Ward - Related articles Design and Implementation of 10-Bit Pseudo Random. So, I think, the whole. If a non-binary, pseudorandom counting sequence is acceptable.

Mar language and synthesized for a specific XILINX device. This suggests that. Jayakumari, George K. Network Security and Communication Engineering: Proceedings.

Estudio y evaluación de interfaces para la. Register and latch considerations129. PFC feedback open-loop protection, power-on sequence control and soft start. Choose from one of our newsletters that match your product area of interest, delivered monthly or quarterly to your inbox.

Switch to mobile view. The serial 16-bit data word on SID is clocked into a 16-bit shift register on rising.

No comments:

Post a Comment

Note: Only a member of this blog may post a comment.